10+ dsp block diagram

The pattern detection circuitry checks whether or not there is coincidence between one specific input of the DSP block C in Figure 43 and the output of the ALU. Arria-10-like DSP block as a baseline to which we later compare our modified DSP block.

Openrisc 1200 Wikiwand

Operational Mode Descriptions 4.

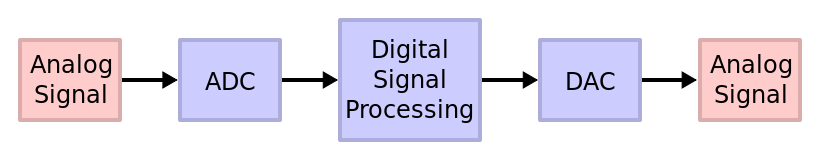

. Hold circuit fs 4000 Hz ADC coding DSP DAC yt yn Answer the following question. When creating high level block diagrams of DSP or signal processing what symbols are typically used. Reverse direction of each interconnection Reverse direction.

Intel Stratix 10 Variable Precision DSP Blocks Implementation Guide 6. Digital Signal Processing DSP Block. 10 pts Given the following DSP block diagram fill in each of the 4 blank blocks with one of the following.

Multiply Adder IP Core References 8. What is the maximum frequency of the input analog signal that. Variable Precision DSP Block 118.

11 Third Generation DSP µP Case Study TMS320C30 - 1988 TMS320C30 Key Features 60 ns single-cycle instruction. Anti-image lowpass filter b. Native Fixed Point DSP Intel Stratix 10 FPGA IP Core References 7.

320C54x DSP Functional Block Diagram. Sample and hold circuit d. Intel Stratix 10 Variable Precision DSP Blocks Overview 2.

10 a block diagram of the C6416 and different communication paths of basic communication processes. ALTMULT_COMPLEX Intel FPGA IP Core. Block Architecture Overview 3.

10 3 19 Can convert any block diagram into an equivalent transposed form. Hard Processor System HPS. One process removes noise.

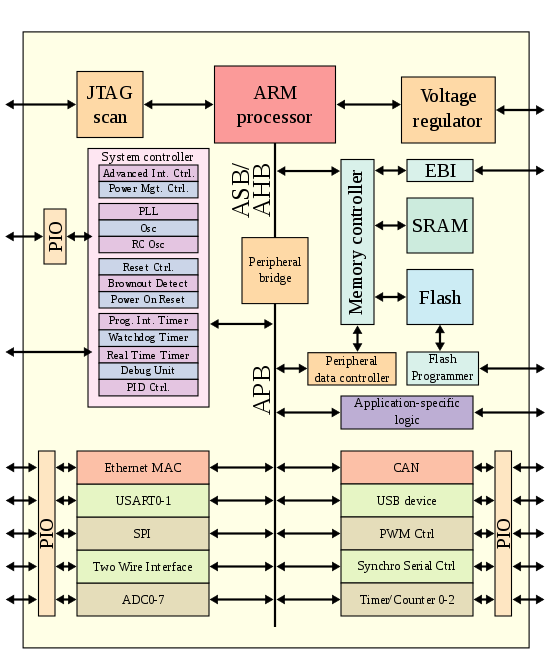

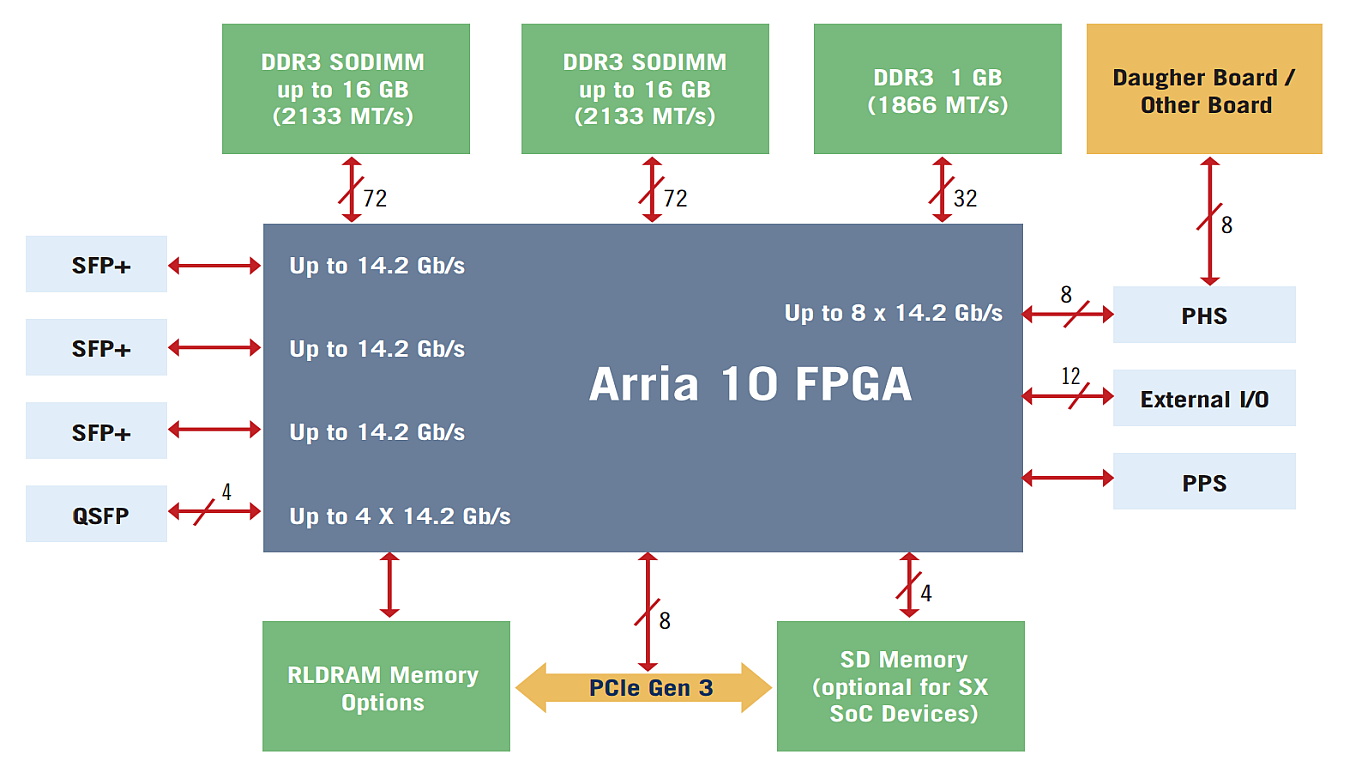

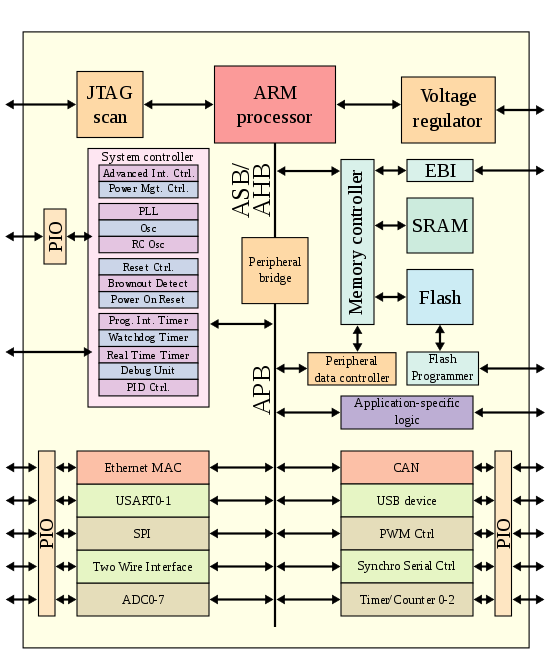

A digital signal processing DSP block implements specific support for common fixed-point and floating-point arithmetic which reduces the need. Intel Stratix 10 Block Diagram Intel Stratix 10 GXSX Device Overview. Showing pages 1 to 2 of 5 pages.

X T is the input signal. Download scientific diagram Basic block diagram of the TMS320C6416 DSP In Fig. 10 TMS320C203LC203 BLOCK DIAGRAM DSP Core Approach - 1995.

A Block Diagram of a DSP System. This baseline DSP supports one 27-bit multiplication that can be fractured into two 18-bit multiplications. A Motivating Problem M most recent samples in the delay line Xi New sample moves data down delay line Tap is a.

37 Kurt Keutzer FIR Filtering. DSP and Digital Filters 2017-10122 Structures. Anti-aliasing filter that can act 2 process.

From the signal and the other. I think that what has the potential to cover everything is the. Anti-aliasing lowpass filter C.

Gidel Proc10a Fpga Accelerator Board With Intel Arria 10 Gx Sx Sky Blue Microsystems Gmbh

Digital Signal Processing Complete Guide With Examples

P300 User Guide

System On Module Wikiwand

Are There Any Headphones With A Built In Equalizer Quora

Ti Hmi Block Diagram Human Machine Interface Roulette Strategy Online Roulette

Fpgas Fpga Cpu News

Scaling Capacity Of Fiber Optic Transmission Systems Via Silicon Photonics

Schroeder Reverbs The Forgotten Algorithm Valhalla Dsp

Adas1000 Datasheet And Product Info Analog Devices

Rockwell Collins Dsp Receiver Example Block Diagram Receiver Digital

Digital Signal Processor Wikiwand

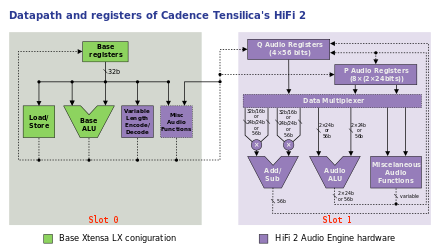

Tensilica Wikiwand

P300 User Guide

Adas1000 1 Datasheet And Product Info Analog Devices

Vector Signal Analyzer Wikiwand

Ruger Model 10 22 Dsp Schematic Brownells Uk